Ausgangspunkt und Aufgabenstellung

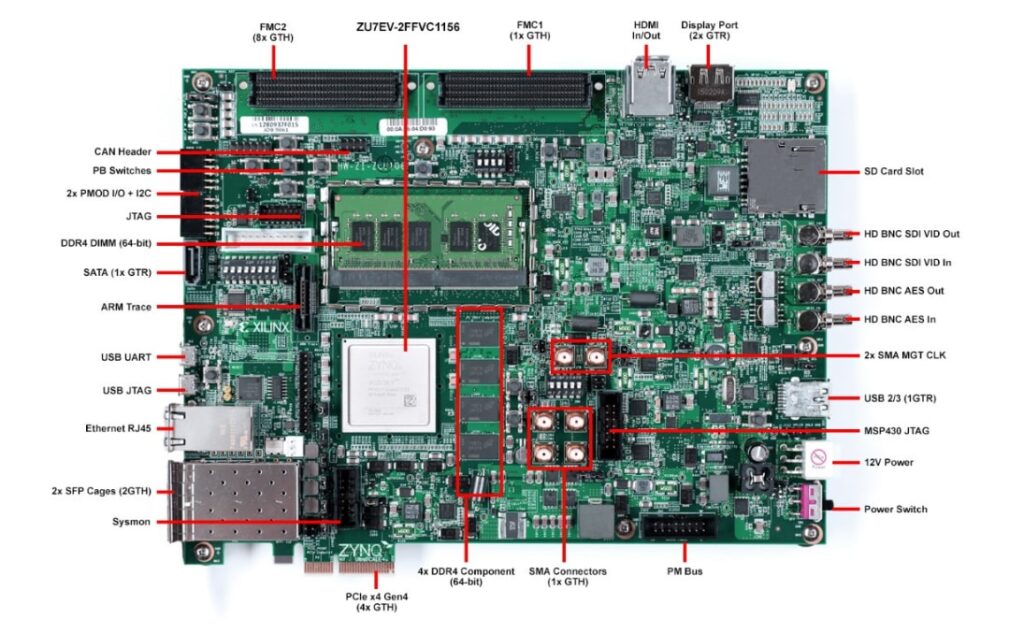

Schnittstellen wie DisplayPort, HDMI/DVI und SDI, die im Videobereich den Standard darstellen, verwenden allesamt schnelle serielle Kommunikationskanäle mit Datenraten im Bereich bis zu einigen Gbit/s. Die speziellen Hardwareeinheiten, die zum Senden und Empfangen bei diesen Frequenzen notwendig sind, sind typischerweise auf Hochleistungs-FPGAs verfügbar. Eine FPGA-Familie, die beispielsweise Datenraten zulässt, wie sie von DisplayPort 1.4 benötigt werden ist die UltraScale+-Familie von Xilinx. Damit sind Auflösungen von 8k bei einer Wiederholfrequenz von 60 Hz und Komprimierung möglich. Im Projekt wird hierzu das Entwicklungsboard ZCU 106 von Xilinx zur Verfügung stehen.

Im Rahmen des Projekts sollen für dieses FPGA-Board IP-Cores zur Verarbeitung eines Videostroms erstellt werden. Mit diesen soll ein Videosignal generiert oder verarbeitet werden. Es soll möglich sein Videosignale von HDMI oder Displayport zu empfangen und die resultierenden Videosignale wieder ausgeben zu können. Um in Zukunft rohe Videoströme aufzeichnen oder abspielen zu können soll parallel ein Adapter erstellt werden mit dem Datenströme auf eine NVMe-SSD geschrieben oder auch wieder ausgelesen werden. Das soll zur Maximierung der Performance ebenfalls in Hardware erfolgen.

Teilziele

- Einarbeiten in die aktuell bestehende Video-Signalverarbeitungsplattform auf Basis des ZCU 106 und in die Verwendung von Xilinx Vivado als FPGA-Entwicklungssystem

- Ergänzung der Videosignalverarbeitungskette unter Verwendung fertiger Verarbeitungsblöcke von Xilinx

- Entwicklung eigener Videosignalverbeitungsblöcke mit AXI-Streaming-Schnittstelle unter Verwendung von VHDL bzw. unter Verwendung von C/C++ mittels High-Level-Synthese.

- Speichern und Abrufen von Datenströmen auf hochperformante SSD (NVMe-Standard auf Basis von PCIe)

Themenfelder

- FPGA-Design und IP-Core-Design mit AXI-Bus für Xilinx FPGAs

- HDMI 2.0

- Signalverarbeitung

- Videosignalverarbeitung

- High-Level-Synthesis

Projektteam

- Michael Wurm

- Mathias Dittrich

- Samuel Hick (Nur erste Hälfte vom Projekt)

- Sebastian Kaupper

- Paul Götzinger

Betreuer

- FH-Prof. DI Dr. Markus Pfaff

- Jakob Winkler MSc

Partner

- FH OÖ F&E

- Fa. AV Stumpfl, Wallern

- SAL – Silicon Austria Labs, Linz

Umsetzung

Von Beginn an wurde Continuous Integration (CI) in Verbindung mit einem Build-Server eingesetzt. Dadurch wurden alle auf den GitLab-Server gepushte Commits sofort synthetisiert. Da sich die von Xilinx Vivado erstellten Projekte schlecht für den Einsatz in einer Versionsverwaltung eignen, wurde aus dem Projekt ein Skript generiert mit dem das eigentliche Projekt erstellt wird. Dadurch konnte auch die Verzeichnisstruktur angepasst werden um generierte Dateien besser aus der Versionsverwaltung ausnehme zu können. Für die Themen Videoverarbeitung und NVMe haben wir uns innerhalb des Projektteams in zwei Gruppen geteilt und getrennt die Aufgabenstellungen behandelt.

Bei der Videoverarbeitung wurde zuerst mit dem FPGA Board PYNQ Z2 gestartet, da dieses einen einfacheren FPGA aufweist. Dadurch konnten kleinere Synthese Zeiten erreicht werden. Mit diesem Board war es bereits möglich Videosignale einzulesen und auszugeben sowie das Audiosignal vom Videosignal zu trennen. Im nächsten Schritt wurden die gewonnen Erkenntnisse genutzt und die Arbeit mit dem ZCU106 fortgesetzt. Für dieses wurde ein Testbildgenerator erstellt. Mit diesem ist es auch ohne externer Videosignalquelle möglich Videoverarbeitung durchzuführen beziehungsweise diese zu testen. Über eine serielle Schnittstelle wurde die Konfiguration der Auflösung und der Videosignalquelle implementiert.

Die Videoverarbeitung wurde mit der Erstellung von IP-Blöcken mittels High Level Synthesis (HLS) fortgesetzt. Mit dieser kann C/C++-Code in Hardware übersetzt werden. Als erstes Beispiel wurde das Invertieren der Farben des Bildes implementiert. HLS wurde weiters zur Erstellung eines weiteren Testbildgenerators genutzt der das Standard EBU-Farbbalken Testbild implementiert. Zuletzt wurde ein Mandelbrot Generator implementiert. Bei diesem wurde auch speziell auf Ressourcenoptimierung geachtet.

Bei der Anbindung der NVMe-SSD an den FPGA wurde diese zuerst an den Prozessor im FPGA angebunden und mit dem Linux-System angesprochen. Die Entwicklung einer eigenen NVMe Schnittstelle wurde zuerst Schrittweise im Linux-System durchgeführt und anschließend in ein RTL-Design übertragen. Im ersten Schritt wurde unter Linux ein Tool eingesetzt um direkt Befehle an den NVMe-SSD absetzen zu können. In weiteren Schritten wurde ein eigenes Tool erstellt, um die NVMe SSD anzusprechen. Dieses wurde nach und nach erweitert bis alle benötigten Funktionen implementiert waren. Dazu gehört die Initialisierung und Konfiguration der SSD und in Folge Lesen und und Schreiben von Daten. Durch die parallele Nutzung des NVMe-Treibers vom Linux-Kernel, war es nicht notwendig ein voll funktionsfähiges Tool von Anfang an zu haben. Dadurch konnten Tests weiter durchgeführt werden. Die Erkenntnisse wurden anschließend genutzt, um die Initialisierung und Nutzung der NVMe-SSDs in Hardware zu ermöglichen.

Resultate

- Reproduzierbare Build- und Testumgebungen mit Skripten

- Implementierung eines Datenpfads zur Videoverarbeitung

- Serielle Schnittstelle zur Konfiguration des Datenpfads während der Laufzeit

- Invertierung eines Videosignals

- Erzeugung von Testbildern und Mandelbrot Fraktalen

- Initialisierung und Konfiguration des NVMe-Controllers vom FPGA

- Steuerung des NVMe Adapters vom Linux-System

Herausforderungen und gewonnene Erkenntnisse

- Der Aufbau der Continuous Integration war zwar zeit- und arbeitsaufwendig, hat aber die weitere Entwicklung vereinfacht

- Die Erstellung von automatisierten Testfällen ist aufwendig, hilft jedoch Fehler frühzeitig zu finden.

- Das Übertragen von C++ Anwendungen zu VHDL ist ohne HLS sehr aufwendig

- Xilinx Vivado bietet nach erstmaliger Einrichtung mächtige Werkzeuge, um Fehler im Design zu finden

- Die Arbeit mit großen FPGAs ist aufgrund der langen Synthesezeiten sehr mühsam

- HLS benötigt einiges an Einarbeitung, um die Zusammenhänge zwischen C++ Code und resultierendem VHDL zu verstehen

GitLab Repository

Das gesamte Projekt, inklusive ausführlicher Beschreibungen und Anleitungen in READMEs, kann in folgendem GitLab Repository gefunden werden:

(Hinweis: Das Repository ist am internen GitLab Server der FH Hagenberg bereitgestellt. Somit muss gegebenenfalls eine Freigabe erfolgen, um Zugriff auf den Inhalt zu bekommen).

https://gitlab.fh-ooe.at/esd/videosigxilinx/